# **Universidad del Azuay**

# Facultad de Ciencia y Tecnología

Escuela de Ingeniería Electrónica

Diseño e implementación de una red Zigbee de módulos de Adquisición de datos y control multifunción, basados en microcontrolador

Trabajo de graduación previo a la obtención del título de Ingeniero Electrónico

> Autores: David Lizardo Lasso Rodríguez Christian Geovanny León Carpio

Director: Freddy Gonzalo Pesantez Díaz

Cuenca, Ecuador 2013 **DEDICATORIA**

A:

Dios por permitirme despertar cada día, después de mis errores y aciertos, por darme la oportunidad de enfrentar obstáculos, por poner cada evento y persona en mi camino para mostrarme el amor y la gracia de vivir.

Mi madre que nunca ha dejado de guiarme y cuando todas las puertas podían haberse cerrado ella nunca se apartó, es mi apoyo y consejera de cada día, de toda mi vida, no sería nada sin su amor.

A mi Padre, hermanas y sobrina son motores que mueven mi vida, que han llenado cada instante de felicidad y por quienes quiero seguir adelante.

A mi Abuelita, tíos y primos que son mi ejemplo de lucha y entrega por la familia.

A mi novia y amigos con quienes he pasado momentos bellos y difíciles, en quienes confío y me apoyo para el resto de mi vida.

A todas las personas que han llegado a mi vida, a quienes no he nombrado pero sin duda nada sería igual.

Esto lo dedico a Ustedes...

Atentamente:

David Lasso Rodríguez.

# **DEDICATORIA**

Quiero dedicar este proyecto de tesis a todas las personas que han estado pendientes del mismo a lo largo de su desarrollo, incluyendo familiares docentes, amigos y principalmente a Dios por poner en mi camino a todos aquellos en mención.

Especialmente este proyecto va dirigido hacia mis padres que han hecho un gran esfuerzo por sacarme adelante y darme una educación de calidad, empezando por los valores inculcados desde casa.

A mi esposa que me ha apoyado incondicionalmente para culminar mis estudios a pesar de los obstáculos que hemos tenido que atravesar, a mis dos hijas que han sido una inspiración y la fuerza para poder continuar, pensando en un mejor futuro para ellas mi esposa y mío mismo.

A mis hermanas, tíos, abuelos y primos que siempre han estado pendientes de mi proyecto e interesados en los inconvenientes que he pasado durante su desarrollo.

# **AGRADECIMIENTOS**

Los agradecimientos generados en este trabajo de tesis se presentan en conjunto por parte de los autores.

A la Universidad del Azuay por haber puesto a nuestra disposición, sus recursos, su personal para que los conocimientos sean adquiridos de la manera más apta y dichos conocimientos sean el apoyo de cada uno en su desarrollo profesional y personal.

Al Msc. Freddy Pesantez, director del proyecto de tesis que a lo largo del desarrollo nos ha sabido guiar oportuna, amable y competentemente, para así lograr una adecuada estructuración de los objetivos versus el resultado final.

A los miembros del jurado cuyos comentarios y sugerencias han sido invaluables desde el momento del diseño hasta la culminación del proyecto.

Atentamente:

Los Autores.

# **INDICE DE CONTENIDOS**

| Dedicatoria                                               | ii  |

|-----------------------------------------------------------|-----|

| Dedicatoria                                               | iii |

| Agradecimientos                                           | iv  |

| Índice de contenidos                                      | ٧   |

| Indice de Anexos                                          | X   |

| Resumen                                                   | xi  |

| Abstract                                                  | xii |

| Introducción                                              | 1   |

| CAPITULO 1: FUNDAMENTOS TEÓRICOS                          |     |

| Introducción                                              | 4   |

| 1.1 Dispositivos de adquisición y control de datos en red | 4   |

| 1.2 Descripción de protocolos inalámbricos orientados al  | 5   |

| campo industrial                                          |     |

| 1.2.1 Bluetooth                                           | 6   |

| 1.2.2 WIFI                                                | 7   |

| 1.3 Zigbee                                                | 8   |

| 1.3.1Objetivo de Zigbee                                   | 8   |

| 1.3.2 Características                                     | 8   |

| 1.3.3 Elementos en un red Zigbee                          | 9   |

| 1.3.4 Topologías Zigbee                                   | 9   |

| 1.3.5 Campos de aplicación Zigbee                         | 10  |

| 1.4 Estudio comparativo entre estándares Bluetooth, WIFI  | 12  |

| y Zigbee                                                  |     |

| 1.5 Módulos de comunicación inalámbrica Xbee series2      | 14  |

| 1.6 Microcontroladores                                    | 16  |

| 1.6.1 Conceptos preliminares                              | 16  |

| 1.6.1.1 Ciclo de máquina (CM)                             | 16  |

| 1.6.1.2 Ciclo de instrucción (CI)                         | 16  |

| 1.6.1.3 Registros                                          | 17 |

|------------------------------------------------------------|----|

| 1.6.1.4 Registro de datos o de propósito general           | 17 |

| 1.6.1.5 Registro de control o de propósito específico      | 17 |

| 1.6.2 Memorias                                             | 18 |

| 1.6.2.1 Memoria para datos                                 | 18 |

| 1.6.2.2 Memoria para programas                             | 19 |

| 1.6.3 Especificaciones y estructura física de la memoria   | 19 |

| de datos                                                   |    |

| 1.6.3.1 Registros de control                               | 19 |

| 1.6.4 Módulo EUSART                                        | 20 |

| 1.6.4.1 Modo asíncrono                                     | 21 |

| 1.6.4.2 Modo síncrono                                      | 21 |

| 1.6.4.3 Trasmisor asíncrono                                | 21 |

| 1.6.4.4 Receptor asíncrono                                 | 22 |

| 1.6.5 Conversor analógico/digital                          | 23 |

| 1.6.6 Módulo MSSP                                          | 24 |

| 1.7 Módulo MCP4725                                         | 24 |

| CAPITULO 2: DISEÑO DE HARDWARE                             |    |

| Introducción                                               | 26 |

| 2.1 Esquema general modulo de adquisición y control        | 26 |

| 2.2 Circuito básico de funcionamiento del microcontrolador | 27 |

| 18f4553                                                    |    |

| 2.2.1 Alimentación                                         | 28 |

| 2.2.2 Señal de reinicio                                    | 28 |

| 2.2.3 Señal de reloj                                       | 28 |

| 2.3 Protecciones para sobre-voltajes en pines I/O          | 29 |

| 2.3.1 Diodo Zener                                          | 30 |

| 2.3.2 Comparador de voltaje                                | 35 |

| 2.3.3 Generación de alarmas en circuito de protección      | 37 |

| 2.4 Implementación física de Universal Serial Bus (USB)    | 38 |

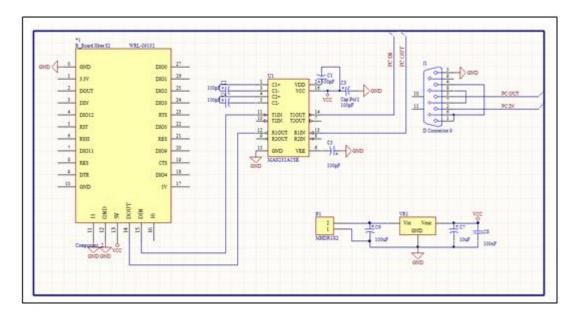

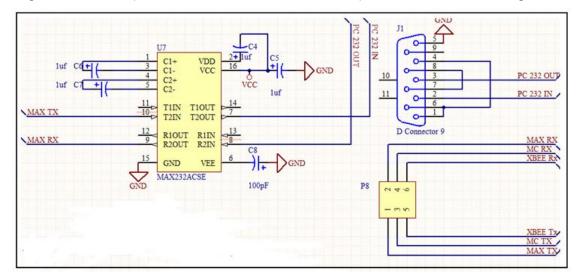

| 2.5 Conexión RS232                                         | 40 |

| 2.6 Comunicación inalámbrica en red                            | 44 |

|----------------------------------------------------------------|----|

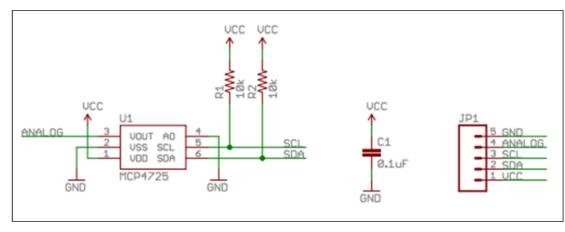

| 2.7 Salidas analógicas                                         | 46 |

| 2.7.1 Salida analógica controlada mediante puerto serial I2C   | 47 |

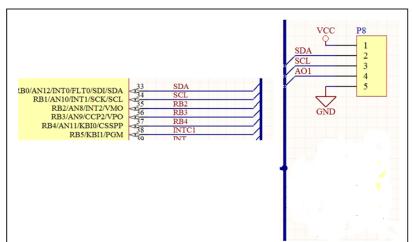

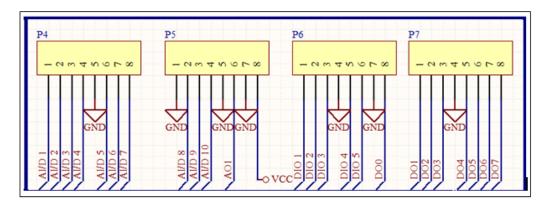

| 2.8 Distribución y organización de puertos                     | 49 |

| 2.9 Desarrollo de hardware del módulo de adquisición           | 50 |

| 2.10 Desarrollo de hardware del módulo coordinador             | 50 |

| CAPITULO 3: DISEÑO DE FIRMWARE, SOFTWARE Y RED DE ADQUISICIÓN  |    |

| Introducción                                                   | 53 |

| 3.1 Códigos de configuración, envío y solicitud de información | 53 |

| 3.2 Clasificación de líneas de puerto por grupos               | 55 |

| 3.2.1 Clasificación por sentido de la información              | 55 |

| 3.2.1.1 Codificación para solicitud de información             | 57 |

| 3.2.1.2 Codificación para envío de información                 | 58 |

| 3.3 Información adicional para salidas digitales               | 60 |

| 3.4 Códigos de configuración y envío de información para       | 61 |

| línea de salida analógica                                      |    |

| 3.5 Desarrollo de firmware del microcontrolador                | 62 |

| 3.5.1 Directivas iniciales y vectores                          | 62 |

| 3.5.2 Variables e inicialización                               | 63 |

| 3.5.3 Configuración de periféricos                             | 64 |

| 3.5.4 Programa principal                                       | 65 |

| 3.5.5 Subrutinas                                               | 65 |

| 3.5.5.1 Subrutina de demora                                    | 65 |

| 3.5.5.2 Subrutina de atención a interrupción                   | 66 |

| 3.5.5.2.1. Subrutinas de configuración de puerto               | 68 |

| 3.5.5.2.2 Subrutina de configuración I2C                       | 76 |

| 3.6 Desarrollo de red de adquisición                           | 79 |

| 3.6.1 Consideraciones previas respecto al coordinador          | 79 |

| 3.6.2 Módulos Xbee                                             | 79 |

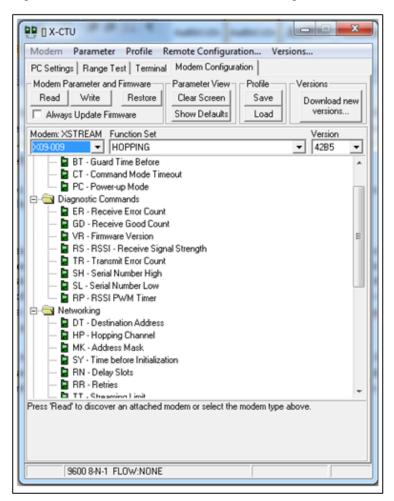

| 3.6.2.1 Interfaces para configuración de módulos Xbee          | 81 |

| 3.6.2.2 XbeeConfig Tool                                        | 81 |

| 3 6 2 3 X-CTU                                                  | 82 |

|     | 3.6.3 Desarrollo de un terminal serial de código propio  | 83  |

|-----|----------------------------------------------------------|-----|

|     | en Labview®                                              |     |

|     | 3.6.3.1 Coolterm                                         | 83  |

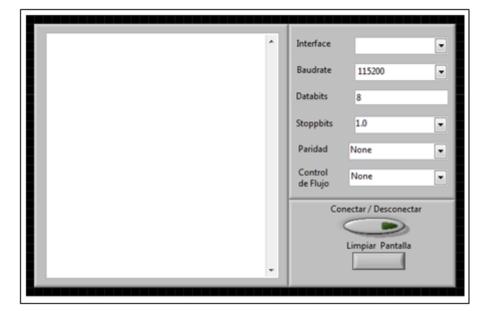

|     | 3.6.3.2 Desarrollo terminal serial en Labview®           | 84  |

|     | 3.6.4 Manejo de registros de configuración módulos Xbee  | 85  |

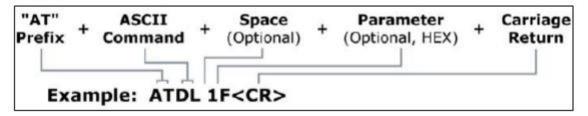

|     | 3.6.4.1Comandos AT                                       | 85  |

|     | 3.6.4.2 Estructura de un comando AT                      | 85  |

|     | 3.6.4.3 Suit de comandos AT                              | 86  |

|     | 3.6.5 Configuración de Xbee como coordinador de red      | 88  |

|     | 3.6.6 Configuración de Xbee como dispositivo final       | 92  |

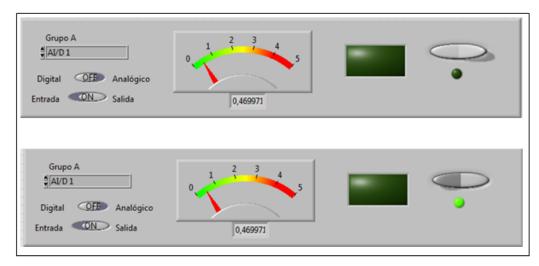

| 3.7 | Desarrollo de software de prueba en Labview®             | 93  |

|     | 3.7.1 Desarrollo de interface grafica (panel de control) | 94  |

|     | 3.7.1.1 Grupo A                                          | 95  |

|     | 3.7.1.2 Grupo B                                          | 96  |

|     | 3.7.1.3 Grupo C                                          | 97  |

|     | 3.7.1.4 Grupo D                                          | 97  |

|     | 3.7.1.5 Selección de líneas y funciones                  | 97  |

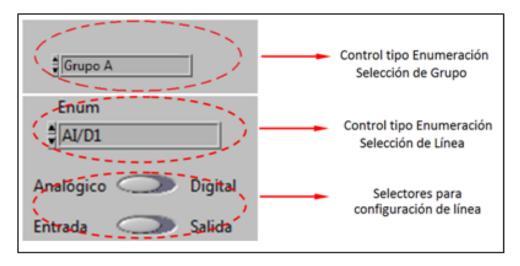

|     | 3.7.1.6 Controles tipo enumeración                       | 98  |

|     | 3.7.1.7 Selectores                                       | 98  |

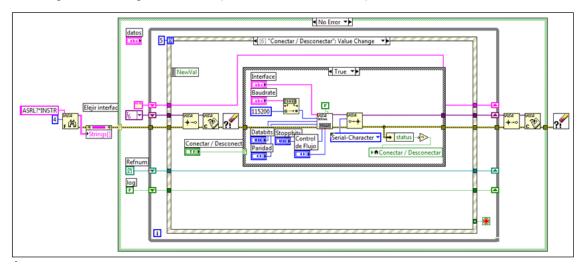

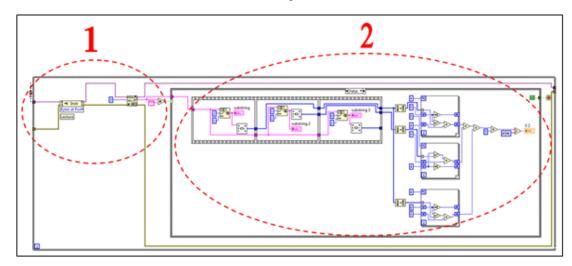

|     | 3.7.2 Desarrollo de programación (diagrama de bloques)   | 99  |

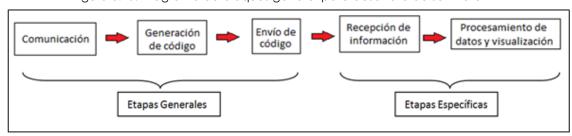

|     | 3.7.2.1 Diagrama general de software para adquisición y  | 99  |

|     | control                                                  |     |

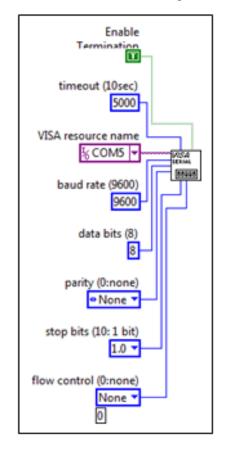

|     | 3.7.2.2 Comunicación                                     | 100 |

|     | 3.7.2.3 Inicialización y configuración de puerto serial  | 100 |

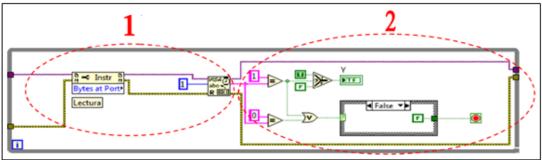

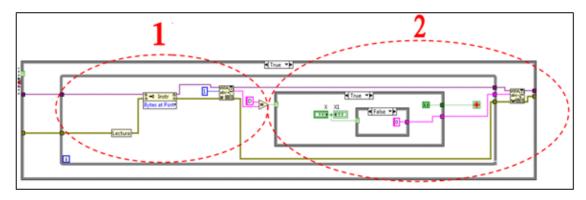

|     | 3.7.2.4 Escritura y lectura                              | 101 |

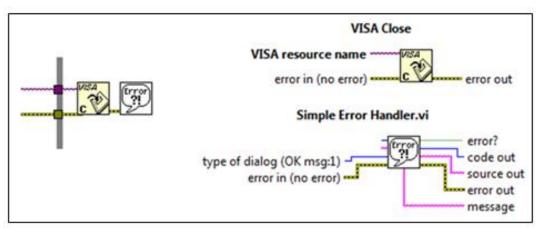

|     | 3.7.2.5 Cierre de sesión de comunicación                 | 102 |

|     | 3.7.2.6 Generación de código                             | 102 |

|     | 3.7.2.7 Envío de código                                  | 103 |

|     | 3.7.2.8 Software para adquisición de líneas de entrada   | 104 |

|     | analógica (solicitud de información)                     |     |

|     | 3.7.2.9 Software para adquisición de líneas de entrada   | 106 |

|     | digital (solicitud de información)                       |     |

|     | 3.7.2.10 Software para adquisición de líneas de salida   | 106 |

|   | analógica (envío de información)                              |     |

|---|---------------------------------------------------------------|-----|

|   | 3.7.2.11 Software para adquisición de líneas de salida        | 108 |

|   | digital (envío de información)                                |     |

|   |                                                               |     |

| C | APITULO 4: PRUEBAS, RESULTADOS Y CONCLUSIONES                 |     |

|   | Introducción                                                  | 109 |

|   | 4.1 Prueba de funcionamiento para configuraciones especificas | 109 |

|   | de línea                                                      |     |

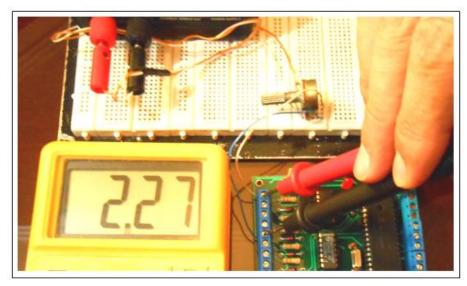

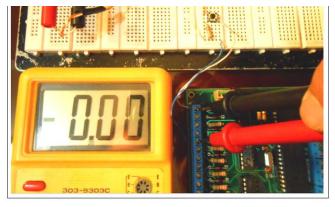

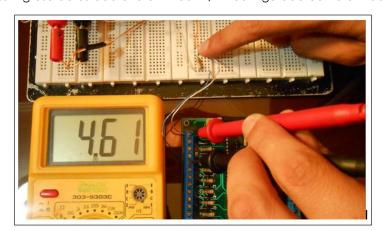

|   | 4.1.1 Prueba para línea multifunción                          | 109 |

|   | 4.1.1.1 Prueba de línea multifuncional como entrada           | 110 |

|   | analógica                                                     |     |

|   | 4.1.1.2 Prueba de línea multifuncional como entrada           | 111 |

|   | digital                                                       |     |

|   | 4.1.1.3 Prueba de línea multifuncional como salida digital    | 112 |

|   | 4.1.2 Línea de función única (salida analógica)               | 113 |

|   | 4.1.3 Resultado                                               | 114 |

|   | 4.2 Prueba de funcionamiento de alarma contra sobre-voltajes  | 115 |

|   | 4.2.1 Resultados                                              | 116 |

|   | 4.3 Prueba de calidad de transmisión y recepción inalámbrica  | 116 |

|   | 4.3.1 Resultados                                              | 118 |

|   | 4.4 Conclusiones                                              | 119 |

|   | 4.5 Recomendaciones                                           | 120 |

|   | 4.6 Análisis de Costos                                        | 121 |

|   |                                                               |     |

|   | Bibliografía                                                  | 122 |

|   | Anexos                                                        | 123 |

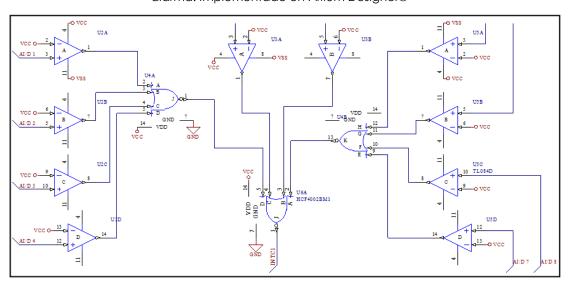

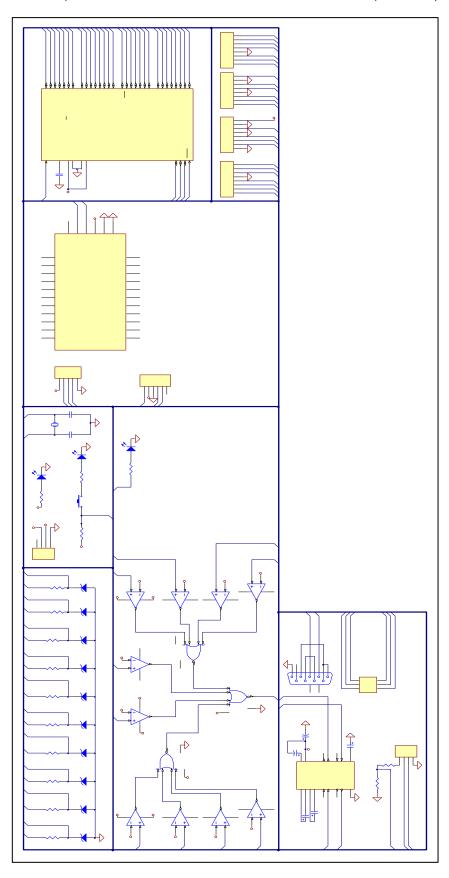

| Anexo 1 Diagrama esquemático del hardware         | 123 |

|---------------------------------------------------|-----|

| de modulo de adquisición y control                |     |

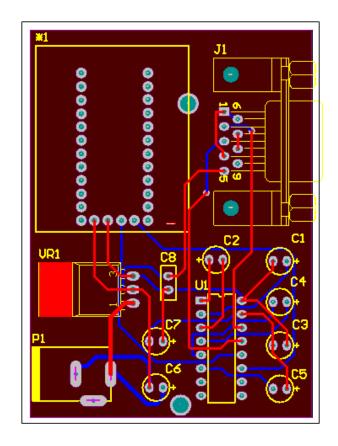

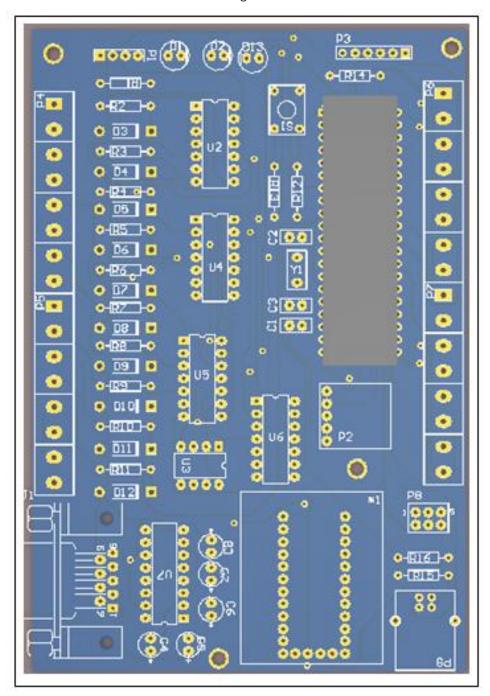

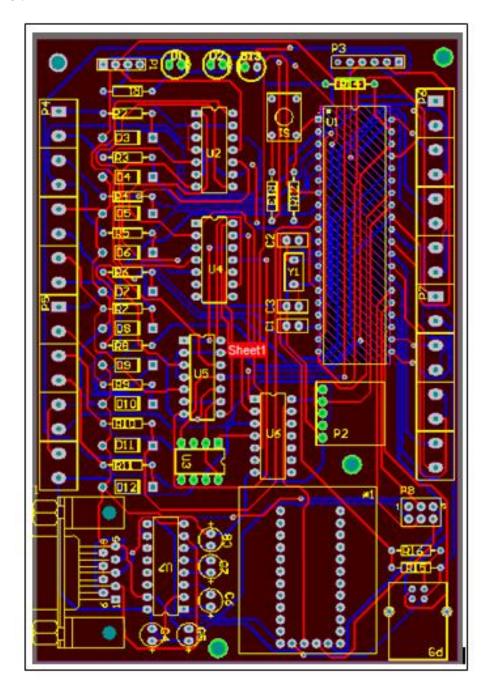

| Anexo 2 Captura de imagen del PCB correspondiente | 124 |

| al módulo de adquisición y control                |     |

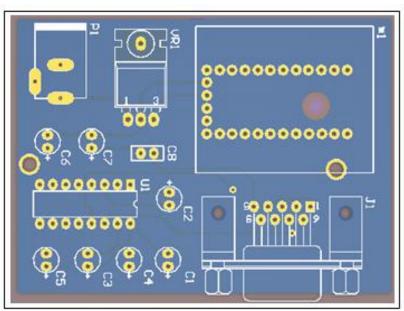

| Anexo 3 Diagrama esquemático y captura de imagen  | 125 |

| del PCB correspondiente al modulo coordinador     |     |

# RESUMEN DEL TRABAJO DE TESIS DE DISEÑO E IMPLEMENTACIÓN DE UNA RED ZIGBEE DE MÓDULOS DE ADQUISICIÓN DE DATOS Y CONTROL MULTIFUNCIÓN, BASADOS EN MICROCONTROLADOR.

Para diseñar e implementar el hardware, software y firmware relacionados a los componentes de la red de módulos inalámbricos de adquisición y control basados en microcontrolador, se sentaron bases teóricas en redes inalámbricas de área personal (WPAN), programación de microcontroladores pic, lenguaje de programación grafico Labview®, electrónica analógica, electrónica digital y manejo de información.

Todos estos fundamentos teóricos complementados con simulaciones y cálculos permitirán el diseño profesional de tarjetas de circuito impreso. Una vez implementados los PCB con componentes correctamente dimensionados, serán sometidos a una serie de pruebas que evaluarán profundamente aspectos de estabilidad, funcionalidad y fiabilidad.

Se demostró que la unión de la multifuncionalidad provista por el microcontrolador, la adaptabilidad de Zigbee, la versatilidad de la programación en Labview y un adecuado diseño de hardware entrega un producto orientado a la industria, competitivo y recomendable.

#### Palabras clave:

Multifuncionalidad, sensorización, MCP4725, sobredimensionamiento, baudios, TXREG, selectores, asíncrono, serializar, reg pin, accionadores.

Ing. Francisco Vásquez

Director Escuela Ingeniería

Electrónica

Ing. Freddy Pesantez Director de proyecto de

Tesis

David Lasso Rodríguez

od: 39343

hristian León Carpi

Cod: 41433

## **ABSTRACT**

# DESIGN AND IMPLEMENTATION OF A ZIGBEE MODULE FOR THE ACQUISITION OF DATA AND FOR MULTIFUNCTION CONTROL, BASED ON MICROCONTROLLER

In order to design and implement the hardware, software, and firmware related to the components of the wireless modules for acquisition and control based on microcontroller, the theoretical bases of wireless personal area network (WPAN) were presented, as well as the programming of the PIC microcontrollers, the language of Labview ®, analogue electronics, digital electronics, and information management.

All these theoretical fundaments, complemented with simulations and calculations, will allow the professional design of printed circuit boards. Once the PCBs are implemented with correctly dimensioned components, they will be subjected to a series of tests that will evaluate stability, functionality, and reliability aspects.

We demonstrated that the multi functionality provided by the microcontroller, the adaptability of the Zigbee, the versatility of Labview programming, and the adequate design of the hardware, will deliver a competitive and worthwhile product.

**Key Words:** Multi functionality, sensor, MCP4725, over dimensioning, bauds, TXREG, selectors, asynchronous, serialize, reg\_pin, actuators.

Ing. Francisco Vásquez

Director of the School of Electronic

Engineering

David Lasso Rodriguez

Cod: 39343

Ing. Freddy Pesantez Director of the Thesis

Project

Christian Leon Carpio

Cod: 41433

Translated by,

Diana Lee Rodas

DPTO. IDIOMAS

Lasso Rodríguez David Lizardo León Carpio Christian Geovanny Trabajo de Grado Ing. Freddy Gonzalo Pesántez Díaz Junio 2013

# DISEÑO E IMPLEMENTACIÓN DE UNA RED ZIGBEE DE MÓDULOS DE ADQUISICIÓN DE DATOS Y CONTROL MULTIFUNCIÓN, BASADOS EN MICROCONTROLADOR

# INTRODUCCIÓN

Comúnmente, en el ambiente industrial se utilizan equipos sumamente costosos para la adquisición remota de información y control sobre ciertos actuadores, ya que tales equipos trabajan sobre protocolos que generalmente se usan para transmisión masiva de datos como WIFI ó Bluetooth. Para una aplicación de sensorización, los protocolos antes citados estarían siendo desperdiciados, por tal razón se pretende utilizar otro protocolo que maneja menores tasas de comunicación y baja latencia. Un protocolo que presenta características que se ajustan a este requerimiento es el protocolo ZIGBEE ("estándar de tecnología inalámbrica para redes de sensores y control, de bajo costo y bajo consumo" [1]).

Los equipos basados en este protocolo son de baja potencia de emisión por lo que se los usa en redes de área personal (PAN), pero así mismo el consumo energético es mínimo por lo que se podrían usar sistemas alternativos de alimentación.

Una de las desventajas al implementar una red de adquisición es cuando se lo hace sobre una infraestructura existente que no ha sido diseñada con determinados parámetros y sobre la cual una instalación de equipos se hace complicada, costosa y poco estética; en este caso un equipo inalámbrico de pequeñas dimensiones físicas facilita mucho el proceso de instalación.

[1]: http://www.zigbee.org/about/abouttecnology/zigbeetecnology.aspx

Una de las limitaciones que se puede citar de los módulos de adquisición existentes en el mercado, es que se tiene un número establecido e invariable de entradas digitales y analógicas; dada esta situación frente a aplicaciones en las cuales haya un crecimiento de la demanda, surgiría la necesidad de adquirir módulos de expansión lo cual genera más costos.

Al observar la problemática citada anteriormente se fundamentará el proyecto en base a los siguientes aspectos:

- El bajo costo que tendría el módulo de adquisición frente a productos similares que se ofertan actualmente en el mercado.

- Transferencia tecnológica, ya que actualmente en nuestro medio no se han implementado de manera documentada proyectos basados en tecnologías como Zigbee, aportando en éste estudio fundamentos teóricos acompañados de resultados prácticos.

- Debido que Zigbee es una solución de protocolo inalámbrico que opera en la banda libre ISM de los 2.4 GHz, no está sujeta a impuestos o pagos por su uso, que son dictados en nuestro país por la Superintendencia de Telecomunicaciones.

- Una arquitectura flexible, eliminará las restricciones relacionadas a una cantidad estática de entradas/salidas analógicas o digitales, ya que se podrá cambiar la configuración de cada puerto según sea la necesidad.

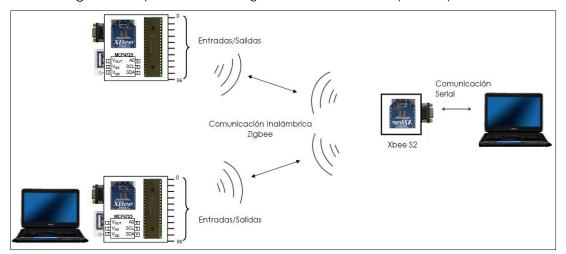

Basados en el análisis de la problemática y de los fundamentos anteriormente expuestos, se pretende diseñar e implementar un módulo de adquisición de datos y control inalámbrico multifunción, programable local y remotamente mediante una red Zigbee cuyo esquema general se muestra en la figura 1.

El módulo de adquisición estará conformado de un embebido Xbee S2 (Protocolo 802.15.4), un Microcontrolador 18F4553 conjuntamente con un conversor digital a analógico MCP4725 y protecciones para los componentes contra sobre-voltajes de entrada; este prototipo poseerá prestaciones como:

- -Líneas Input analógicas.

- -Líneas Input digitales

- -Línea Output analógica.

- -Líneas Output digitales.

- -Puerto serial.

- -Puerto USB (para futuras aplicaciones).

Figura 1. Esquema de la red Zigbee de módulos de adquisición y control.

Se implementarán dos aplicaciones de software denominadas, Terminal serial e Interfaz de prueba, basadas en lenguaje gráfico Labview®.

La primera aplicación servirá para configuración y direccionamiento del módulo inalámbrico con el cual se desea establecer el enlace.

La segunda aplicación servirá para configurar líneas de puerto, adquisición de datos y generación de señales de control para un módulo seleccionado. Ambas aplicaciones se podrán utilizar tanto localmente como remotamente a los módulos de adquisición.

La metodología de trabajo se la define de la siguiente manera; bibliográfica debido a que se necesita recurrir a la investigación de temas como redes Zigbee, microcontroladores, programación en lenguaje gráfico, etc. Analítica ya que es necesario establecer con sólidos fundamentos teóricos el diseño de circuitos. Experimental ya que es necesario realizar la verificación del funcionamiento de la red de adquisición y configuración remota y sintético para demostrar y visualizar adecuadamente los resultados obtenidos.

# CAPÍTULO 1 FUNDAMENTOS TEÓRICOS

#### Introducción

El capítulo 1 establecerá los fundamentos teóricas que marcan el desarrollo del proyecto, dichas bases exponen los temas más representativos en cuanto a sistemas de adquisición y control, protocolos de comunicaciones inalámbricas, estándar de comunicaciones Zigbee, redes de adquisición basados en Zigbee, módulos de transmisión Xbee Serie 2, microcontrolador PIC18F4553 y módulo DAC MCP4725.

# 1.1 Dispositivos de adquisición y control de datos en red

En muchos de los procesos internos dentro del campo industrial, la adquisición de datos y el control han sido siempre piezas fundamentales que permiten el correcto funcionamiento de un sistema de producción.

En el ámbito de la adquisición, se realiza la toma de datos controlada de un proceso o evento, estos datos nos brindarán la información para obtener una respuesta deseada, mediante el uso del control industrial y los dispositivos que estén ligados a este.

De acuerdo al ambiente industrial se hace necesario y fundamental el uso de un dispositivo que esté comprendido por entradas analógicas, entradas digitales, salidas analógicas, salidas digitales, cuyos datos enviados y recibidos serán procesados en una PC, microcontrolador o componentes DSP; los cuales obtienen información de la señal presente en el área industrial y realiza acciones que implican el envío de señales analógicas o digitales hacia dispositivos actuadores.

El sistema requiere además del dispositivo de adquisición, sensores y una PC, los cuales completan el proceso de obtención de una señal y la realización del proceso instrumental respectivo.

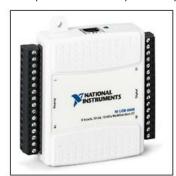

Figura 1.1: Dispositivo de Adquisición y Control

Fuente: Catalogo de productos National Intruments, Multifunction Data Acquisition. <a href="http://sine.ni.com/nips/cds/view/p/lang/es/nid/201987">http://sine.ni.com/nips/cds/view/p/lang/es/nid/201987</a>. [Consulta: 1 de febrero de 2012]

El problema radica al presentarse el aumento en la cantidad de señales presentes y el distanciamiento de las mismas, dentro de un mismo campo. Muchos sistemas de adquisición al enfrentarse a este problema necesitarían de más computadores y elementos. Con la llegada de los dispositivos con protocolos inalámbricos y su adaptación para el control, estos problemas se han visto disminuidos ya que los nuevos dispositivos pueden ubicarse lejos unos de otros, en gran cantidad y siempre tener una comunicación en red proporcionando una confiabilidad y estabilidad del sistema.

# 1.2 Descripción de protocolos inalámbricos orientados al campo industrial

En la actualidad, las comunicaciones inalámbricas han sido identificadas como un pilar fundamental, que abarca desde las tareas más simples desarrolladas en el hogar hasta ámbitos industriales, militares, empresariales, etc. Las características intrínsecas de evolución que las comunicaciones inalámbricas presentan constantemente, han hecho que continuamente se desarrollen mejores capacidades de adaptación a la industria.

Tenemos entonces que para el campo industrial se han adaptado varias tecnologías de comunicaciones inalámbricas tales como:

- Bluetooth.

- WIFI.

- GPRS.

- 3G.

- IRDA.

- ZigBee.

Se realizará a continuación un estudio descriptivo sobre las tecnologías más extendidas y de mayor desarrollo en la actualidad; WIFI, Bluetooth y Zigbee, centrando posteriormente un desarrollo más a fondo en el estándar de comunicaciones Zigbee.

#### 1.2.1 Bluetooth

Inicia en el año de 1998, promovida por empresas como Nokia, Intel y Toshiba. Bluetooth se crea con capacidades de transmisión en la banda libre de los 2.4 GH; además puede conseguir distancias que van desde los 10m hasta los 100m, pero empleando equipos repetidores de señal. Es una tecnología de comunicación, basada en una frecuencia de radio de disponibilidad universal, que permite la creación de pequeñas redes para realizar intercambios de información de manera sencilla.

Bluetooth posee una excelente adaptabilidad a las redes WPAN (Wireless Personal Area Network). Bluetooth ofrece facilidades de establecimiento de canal para transmisión, ya que no posee configuraciones extensas, más que nada se lo ha concebido para eliminar el uso de medios cableados. Esta facilidad también es un limitante al momento de enfrentarse a una red amplia de sensores inalámbricos en un ambiente industrial. La tasa de transmisión es de 720 Kbps por canal.

Figura 1.2 Logo comercial de estándar Bluetooth

Fuente: Pagina oficial de estándar Bluetooth descripciones técnicas y dispositivos. <a href="http://www.bluetooth.com">http://www.bluetooth.com</a>>. [Consulta: 11 de febrero de 2012]

#### 1.2.2 WIFI

La especificación IEEE 802.11 (ISO/IEC 8802-11), es un estándar internacional que define las características de una red de área local inalámbrica (WLAN). WIFI Alliance es el grupo que maneja las normas y garantiza la compatibilidad entre los diferentes productos que estén regidos al estándar 802.11. A los dispositivos certificados por la Wi-Fi Alliance se les permite usar el siguiente logotipo:

Figura 1.3 Logo comercial de estándar WIFI

Fuente: Pagina oficial de estándar WIFI. <a href="http://www.wi-fi.org/"></a>. [Consulta: 15 de febrero de 2012]

Con Wi-Fi se pueden crear redes de área local inalámbricas de alta velocidad, manteniendo siempre la distancia adecuada entre dispositivos (20 a 50 metros en espacio cerrados y hasta 200 metros en espacio abierto). En la práctica, Wi-Fi admite cualquier otro tipo de dispositivo de alta velocidad con propiedades de conexión también de alta velocidad.

WIFI posee capacidades que lo hacen ideales en redes con grandes cantidades de dispositivos, por lo cual en un área industrial WIFI se convierte en un candidato ideal.

Uno de las desventajas que presenta WIFI es el consumo energético, ya que su protocolo no ha sido desarrollado desde sus comienzos como un protocolo verde. Además, dadas ciertas condiciones en un ambiente industrial en el que la adquisición de datos no se la haga de manera constante, WIFI quedaría sobredimensionado ya que las características intrínsecas de este protocolo son de transmisión masiva de datos a grandes velocidades y de manera constante.

# 1.3 Zigbee

"ZigBee es un estándar de comunicaciones inalámbricas diseñado por la ZigBee Alliance. Zigbee no debe ser confundido con una tecnología, sino un conjunto estandarizado de soluciones en comunicaciones orientadas a redes PAN, que pueden ser implementadas por cualquier fabricante. ZigBee está basado en el estándar IEEE 802.15.4 de redes inalámbricas de área personal (wireless personal area network, WPAN)" [2]. Cada producto desarrollado bajo la reglamentación desarrollado por Zigbee Alliance estará autorizado para utilizar el logo comercial.

Figura 1.4: Logo Comercial del estándar Zigbee

Fuente: Pagina oficial del estándar Zigbee y de ZigBee Alliance. < http://www.zigbee.org/>. [Consulta: 15 de febrero de 2012]

# 1.3.1Objetivo de Zigbee

El objetivo del estándar de comunicaciones inalámbrico Zigbee es habilitar redes con capacidades de control y monitoreo con características como escalabilidad y confiabilidad, de bajo consumo energético y de bajo costo, que funcione vía radio y de modo bidireccional, que presenten seguridades como encriptación de información, con baja tasa de envío de datos y maximización de la vida útil de sus baterías.

### 1.3.2 Características

Algunas de las características de ZigBee son:

- ZigBee opera en las bandas libres ISM (Industrial, Scientific & Medical) de 2.4 GHz, tiene una velocidad de transmisión de 250 Kbps y un rango de cobertura de 10 a 75 metros.

- A pesar de coexistir en la misma frecuencia con otro tipo de redes como WIFI o Bluetooth, su desempeño no se ve afectado, esto debido a su baja tasa de transmisión y a características propias del estándar IEEE 802.15.4.

[2]: VALVERDE Jorge, El estándar inalámbrico Zigbee, Perú, Universidad Nacional de Trujillo, 2007

- Capacidad de operar en redes de gran densidad, esta característica ayuda a aumentar la confiabilidad de la comunicación.

- Cada red ZigBee tiene un identificador de red único, lo que permite que coexistan varias redes en un mismo canal de comunicación sin ningún problema.

# 1.3.3 Elementos en una red Zigbee

Se definen tres tipos diferentes de dispositivos ZigBee según su papel en la red:

- "Coordinador ZigBee (ZigBee coordinator, ZC). El tipo de dispositivo más completo. Puede actuar como director de una red en árbol, así como servir de enlace a otras redes y puede almacenar información del sistema. Existe exactamente un coordinador por cada red" [3].

- "Router ZigBee (ZR). Además de ofrecer un nivel de aplicación para la ejecución de código de usuario, puede actuar como router interconectando dispositivos separados en la topología de la red" [4].

- "Dispositivo final (ZigBee end device, ZED). Posee la funcionalidad necesaria para comunicarse con su nodo padre (el coordinador o un router), pero no puede transmitir información destinada a otros dispositivos. De esta forma, este tipo de nodo puede estar dormido la mayor parte del tiempo, aumentando la vida media de sus baterías" [5].

# 1.3.4 Topologías Zigbee

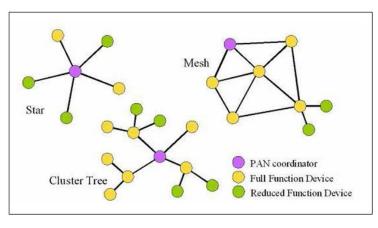

En lo referente a topologías ligadas al estándar de comunicaciones ZigBee, existen tres tipos que con más recurrencia se aplican: estrella, árbol, y red mallada (mesh network), además de las topologías explicadas y presentadas en la figura 1.5, Zigbee presenta flexibilidad y adaptación a las necesidades especificadas de un ambiente en el cual se desea implementar.

[3], [4], [5]: dspace.espoch.edu.ec/bitstream/123456789/1315/1/98T00003.

Figura 1.5 Topologías disponibles para redes Zigbee

Fuente: El estándar inalámbrico Zigbee, Universidad Nacional de Trujillo, Jorge Valverde. <a href="http://es.scribd.com/doc/51196305/ZigBee">http://es.scribd.com/doc/51196305/ZigBee</a> [Consulta: 15 de febrero de 2012]

# Topología estrella

Está conformado por un nodo central que generalmente es un coordinador, al cual están conectados todos los dispositivos finales; dichos dispositivos recurren directamente al coordinador para realizar el intercambio de información entre ellos.

## Topología árbol

Posee un nodo central (Coordinador), al cual recurren los demás nodos formados por dispositivos Full Function Device (Router) y Reduced Funtion Device (End Devices).

# • Topología en malla

Se tiene un nodo central (Coordinador) con el cual se realizan la conexión de enlaces redundantes conformador por routers. Con la finalidad de proporcionar diferentes vías para un mismo destino y así confiabilidad en la red.

#### 1.3.5 Campos de aplicación Zigbee

El mercado para redes ZigBee comprende una amplia variedad de aplicaciones las cuales van de electrodomésticos hasta teléfonos celulares. Es necesario tener en cuenta que ZigBee está diseñado para aplicaciones que transmiten unos cuantos bytes esporádicamente o bajo un pedido, que es el caso de una aplicación para automatizar el hogar (domótica). Una de las áreas de aplicación que ha tomado fuerza, es la de los sistemas

una de las areas de aplicación que na fomado fuerza, es la de los sistemas de medición avanzada, que forman parte de una red con otros dispositivos.

En el campo industrial esta es una de las opciones más eficientes y fáciles de aplicar para sensorización y control.

En la figura 1.6 se presentan los grupos más dominantes de aplicaciones que están en la mira de ZigBee.

Figura 1.6: Diversos grupos de aplicaciones para ZigBee

Fuente: El estándar inalámbrico Zigbee, Universidad Nacional de Trujillo, Jorge Valverde. <a href="http://es.scribd.com/doc/51196305/ZigBee">http://es.scribd.com/doc/51196305/ZigBee</a> [Consulta: 15 de febrero de 2012]

En general, ZigBee resulta ideal para redes estáticas, escalables y con muchos dispositivos, pocos requisitos de ancho de banda y uso infrecuente, y dónde se requiera una duración muy prolongada de la batería. En ciertas condiciones y para determinadas aplicaciones puede ser una buena alternativa a otras tecnologías inalámbricas ya consolidadas en el mercado, como Wi-Fi y Bluetooth, aunque la falta del soporte de TCP/IP no lo hace adecuado por sí solo para la interconexión de redes de comunicaciones IP. Por tanto, la introducción de ZigBee no acabará con otras tecnologías ya establecidas, sino que convivirá con ellas y encontrará sus propios nichos de aplicación.

# 1.4 Estudio comparativo entre estándares Bluetooth, WIFI y Zigbee

Luego de realizar el análisis de cada uno de los tres estándares inalámbricos y relacionar su desarrollo con el campo industrial, procedemos a obtener las siguientes conclusiones:

EL estándar Zigbee es el candidato mejor opcionado para la resolución del proyecto debido a:

- Su consumo energético.

- Su tasa de transmisión de datos.

- Su costo.

- La facilidad de programación y administración de la red.

- La facilidad de adaptabilidad en redes tipo malla.

Si bien WIFI es un protocolo de transmisión que se desarrolla constantemente, es también cierto que las grandes tasas de transmisión, el consumo energético más elevado y la dificultad de adaptabilidad en redes malla lo hacen que sea un estándar no apto para el proyecto.

Se puede decir que Bluetooth se mantiene en ciertos aspectos a la par del estándar Zigbee como el consumo, pero la capacidad de establecimiento de sesión representa un problema ya que Bluetooth necesita tramas de sincronía con los otros dispositivos, lo cual hace que no exista un modo "sleep" como tal y no se aproveche de la mejor manera las baterías o sistemas de alimentación.

Además en cuanto a Bluetooth, cabe recalcar que un problema que se puede presentar es en cuanto a la cantidad de dispositivos que se necesiten en una red y que el costo de los dispositivos no es tan bajo en relación al costo que presenta Zigbee.

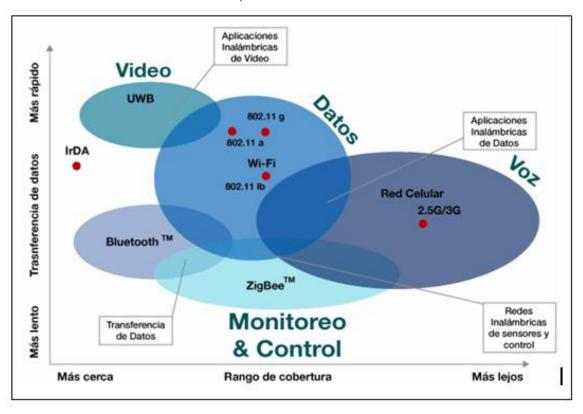

A continuación se presenta la tabla 1.1, que es un análisis comparativo entre los tres estándares anteriormente descritos. Además, la gráfica 1.8 esquematiza los mismos, en criterios de cobertura y transferencia de datos, incluyendo los estándares 3G y UWB (Ultra Wide Band Bluetooth), con aspectos como la tasa de transmisión y la distancia de cobertura.

Tabla 1.1: Comparación Zigbee-WIFI-Bluetooth

| ZigBee                                                                                                                                                                                                                                                   | Bluetooth                                                                                                                                                                                        | Wi-Fi                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (WPAN)                                                                                                                                                                                                                                                   | (WLAN/WPAN)                                                                                                                                                                                      | (WLAN)                                                                                                                                                                                  |

| <ul> <li>Estándar 802.15.4</li> <li>250 kbps</li> <li>TX: 35 mA</li> <li>Standby: 3µA</li> <li>32-60KB memoria</li> <li>Iluminación,<br/>sensores, control<br/>remoto, etc.</li> <li>Red en malla, punto<br/>a punto o punto a<br/>multipunto</li> </ul> | <ul> <li>Estándar 802.15.1</li> <li>1 Mbps</li> <li>TX: 40 mA</li> <li>Standby: 200μA</li> <li>&gt;100KB memoria</li> <li>Telecomunicaciones, audio, etc.</li> <li>Punto a multipunto</li> </ul> | <ul> <li>Estándar 802.11</li> <li>Hasta 54Mbps</li> <li>TX: &gt;400 mA</li> <li>Standby: 20mA</li> <li>&gt;100KB memoria</li> <li>Internet, etc.</li> <li>Punto a multipunto</li> </ul> |

Fuente: El estándar inalámbrico Zigbee, Universidad Nacional de Trujillo, Jorge Valverde. <a href="http://es.scribd.com/doc/51196305/ZigBee">http://es.scribd.com/doc/51196305/ZigBee</a> [Consulta: 15 de febrero de 2012]

Figura 1.8: Grafica comparativa Zigbee-WIFI-Bluetooth-3G-UWB en relación a Rango de cobertura y Transferencia de datos

Fuente: El estándar inalámbrico Zigbee, Universidad Nacional de Trujillo, Jorge Valverde. <a href="http://es.scribd.com/doc/51196305/ZigBee">http://es.scribd.com/doc/51196305/ZigBee</a> [Consulta: 16 de febrero de 2012]

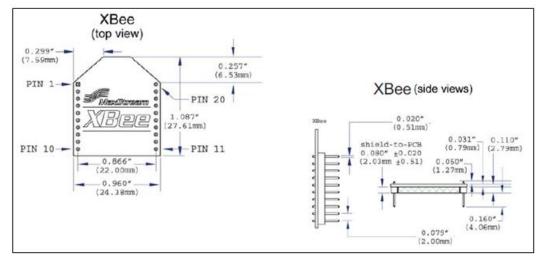

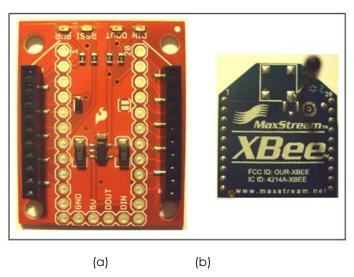

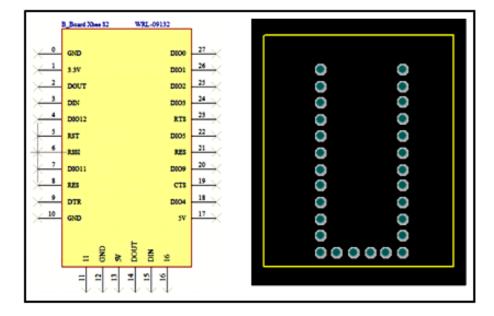

#### 1.5 Módulos de comunicación inalámbrica Xbee Series2

Los módulos de comunicación Xbee fueron diseñados para operar a través del protocolo de comunicaciones ZigBee 802.15.4.

Xbee es solo una de las numerosas empresas que desarrollan productos basados en este protocolo, pero la decisión de optar por estos módulos se basa en la capacidades de creación de redes, configuración, direccionamiento y soporte que estos dispositivos poseen, dichas cualidades son superiores a la mayoría de módulos desarrollados por otras casas fabricantes.

Al basarse Xbee en el protocolo Zigbee estos módulos trabajan en la banda libre ISM 2.4GHz. Además su diseño compacto permite el posicionamiento de estos en ambientes muy reducidos y posee también modos de funcionamiento de bajo consumo o "sleep".

Los módulos Xbee son una alternativa económica frente a los beneficios que pueden brindar ya que cuentan con entradas analógicas, entradas digitales y salidas digitales.

El área que podemos cubrir "Indoor" con estos módulos es de 40 m y 130 m "Outdoor", además esto depende mucho del modelo del módulo Xbee. Se pueden cubrir distancias de hasta 1.6Km con los Xbee Pro, siempre que se tenga línea de vista.

Las temperaturas de funcionamiento fueron pensadas en el campo industrial ya que tienen un rango de -40°C hasta 85°C; además se puede tener teóricamente una red hasta con 65 000 dispositivos y muchas redes diferentes pueden coexistir en un mismo ambiente.

Estos módulos poseen dos tipos de configuraciones:

- Comandos transparentes AT.

- Modo configuración.

Figura 1.9Vistas mecánicas frontal y lateral de módulos Xbee S2

Fuente: XBee™ Series 2 OEM RF Modules.

<ftp://ftp1.digi.com/support/documentation/90000866\_C.pdf> [Consulta: 17 de febrero de

2012]

Tabla1.2: Asignación de Pines para módulos Xbee S2

| Pin # | Name                | Direction | Description                                              |

|-------|---------------------|-----------|----------------------------------------------------------|

| 1     | VCC                 |           | Power supply                                             |

| 2     | DOUT                | Output    | UART Data Out                                            |

| 3     | DIN / CONFIG        | Input     | UART Data In                                             |

| 4     | DIO8                | Either    | Digital I/O 8                                            |

| 5     | RESET               | Input     | Module Reset (reset pulse must be at least 200 ns)       |

| 6     | PWM0 / RSSI / DIO10 | Output    | PWM Output 0 / RX Signal Strength Indicator / Digital IO |

| 7     | PWM / DIO11         | Either    | Digital I/O 11                                           |

| 8     | [reserved]          | -         | Do not connect                                           |

| 9     | DTR / SLEEP_RQ/ DI8 | Input     | Pin Sleep Control Line or Digital Input 8                |

| 10    | GND                 | -         | Ground                                                   |

| 11    | DIO4                | Either    | Digital I/O 4                                            |

| 12    | CTS / DIO7          | Either    | Clear-to-Send Flow Control or Digital I/O 7              |

| 13    | ON / SLEEP          | Output    | Module Status Indicator                                  |

| 14    | [reserved]          | -         | Do not connect                                           |

| 15    | Associate / DIO5    | Either    | Associated Indicator, Digital I/O 5                      |

| 16    | RTS / DIO6          | Either    | Request-to-Send Flow Control, Digital I/O 6              |

| 17    | AD3 / DIO3          | Either    | Analog Input 3 or Digital I/O 3                          |

| 18    | AD2 / DIO2          | Either    | Analog Input 2 or Digital I/O 2                          |

| 19    | AD1/DIO1            | Either    | Analog Input 1 or Digital I/O 1                          |

| 20    | AD0 / DI00          | Either    | Analog Input 0 or Digital I/O 0                          |

Fuente: XBee™ Series 2 OEM RF Modules.

<ftp://ftp1.digi.com/support/documentation/90000866\_C.pdf> [Consulta: 17 de febrero de

2012]

#### 1.6 Microcontroladores

Un microcontrolador es un chip que empaqueta numerosos recursos (periféricos internos) y se comunica al exterior mediante líneas de puerto. Además para su funcionamiento necesita de un circuito oscilador externo que definirá la velocidad con la cual operará el microcontrolador.

Para grabar un programa en un microcontrolador se necesitan de herramientas de hardware y de software. Las herramientas de software están conformadas por editor, compilador y simulador, las mismas que las integra el programa MPLAB® que será utilizado en este desarrollo. Las herramientas de hardware necesarias son, una PC y un grabador de pics.

### 1.6.1 Conceptos preliminares

Para entender el funcionamiento del microcontrolador son necesarios algunos conceptos preliminares. Se pretende referir a las partes básicas de un microcontrolador sobre las cuales se sustenta todo su funcionamiento, como registros, memorias etc.

# 1.6.1.1 Ciclo de máquina (CM)

El Ciclo de Máquina es el espacio de tiempo mínimo que tarda en realizar "una acción" el microcontrolador. Un Ciclo de Máquina (CM) puede o no ser suficiente para ejecutar un comando (instrucción) completo. En los PIC`s un Ciclo de Máquina dura cuatro períodos del Oscilador Externo y ya que éste es de 16MHz, su tiempo es de 0.0625 microsegundos y un ciclo de máquina será de 0.25 microsegundos.

# 1.6.1.2 Ciclo de instrucción (CI)

El Ciclo de Instrucción es el tiempo que demora la ejecución de una instrucción completa; las instrucciones son los comandos que se escriben durante la programación del microcontrolador. Un CI puede requerir de uno o más Ciclos de Máquina (CM) en función de las características de cada instrucción.

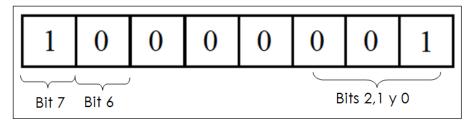

# 1.6.1.3 Registros

Se refiere como registro a un almacenador binario de "n" bits. En el caso específico de los microcontroladores de la familia 18FXXXX, un registro para guardar datos (registro de datos) o información de control (registro de control) es de 8 bits, porque el procesamiento y el transporte de datos se realiza en esas cantidades. Los bits de un registro se enumeran de derecha a izquierda comenzando desde el cero (hasta el 7), siendo el bit 0 "el menos significativo (LSB)" y el bit 7 "el más significativo (MSB)".

REGISTRO.

MSB

7 6 5 4 3 2 1 0

Numeracion de bits

Figura 1.10. Esquema de un registro de un microcontrolador

Fuente: PIC18F2455/2550/4455/4550 Data Sheet.

<a href="http://www.bilbaoelectronics.com/datasheet-pic18f4550.html">http://www.bilbaoelectronics.com/datasheet-pic18f4550.html</a> [Consulta: 17 de febrero de 2012]

# 1.6.1.4 Registro de datos o de propósito general

Como su nombre lo indica un "registro de datos" es un registro que almacena datos necesarios para que el programa se ejecute correctamente, de acuerdo a las necesidades del usuario. Tales registros se encuentran en la Memoria de Datos (tipo R.A.M) o en cualquier memoria auxiliar permanente (tipo FLASH).

# 1.6.1.5 Registro de control o de propósito específico

Un registro de control almacena información necesaria para que el microcontrolador funcione correctamente, adicionalmente algunos de estos registros almacenan también información del estado de funcionamiento o de algún resultado obtenido después de una operación aritmética o lógica. Tales registros se encuentran también en la Memoria de Datos (tipo R.A.M) del microcontrolador, en la parte superior del banco 15.

#### 1.6.2 Memorias

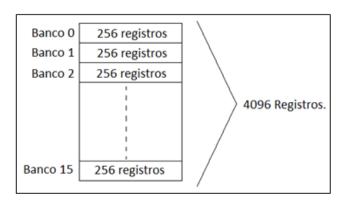

Una memoria está formada por un conjunto organizado de registros de "n" bits. Para el microcontrolador utilizado (18F4553), éstos son de 8 bits y cada uno ocupa una dirección específica dentro de la memoria.

En las memorias modernas (segmentadas) los registros normalmente están agrupados en "bancos" o "páginas", siendo un máximo de 16 los que se pueden disponer en un microcontrolador, tal división se hace con el objetivo de hacer más rápida la búsqueda de información dentro de la memoria.

Figura 1.11. Esquema de una memoria segmentada de 16 bancos con 256 registros cada uno

Fuente: PIC18F2455/2550/4455/4550 Data Sheet.

<a href="http://www.bilbaoelectronics.com/datasheet-pic18f4550.html">http://www.bilbaoelectronics.com/datasheet-pic18f4550.html</a> [Consulta: 17 de febrero de 2012]

#### 1.6.2.1 Memoria para datos

Espacio de memoria dentro del microcontrolador destinado a almacenar información en dos tipos de registro: "de propósito general", donde se almacenan datos necesarios para ejecutar el programa y "de propósito específico" donde se almacenan datos para controlar el funcionamiento del microcontrolador.

Desde el punto de vista tecnológico, las Memorias de Datos pueden ser:

- Volátiles (como la R.A.M).

- Permanentes (como la E.E.P.R.O.M o las de tipo "Flash").

# 1.6.2.2 Memoria para programas

Espacio de memoria dentro del microcontrolador destinado a almacenar, ya sea: los códigos de las instrucciones o comandos, o en algunas aplicaciones también datos permanentes, en las localizaciones que no son ocupadas por los códigos de los comandos. Las memorias de programas son memorias siempre permanentes, porque en un microcontrolador el programa debe ejecutarse una y otra vez, incluso después de haber apagado y encendido el circuito del mismo.

# 1.6.3 Especificaciones y estructura física de la memoria de datos

La Memoria de Datos (RAM) en los microcontroladores 18FXXXX está segmentada o dividida en 16 "bancos" de 256 bytes (256 registros) cada uno. Cada registro está identificado con una dirección única que es un número de 12 bits. Como la dirección de cualquier registro es un número de 12 bits es posible tener como máximo en la Memoria de Datos 4096 registros (2<sup>12</sup> = 4096) en la tecnología 18FXXXX. No todos los microcontroladores de la familia 18FXXXX poseen implementados todos los registros posibles (4096), por ejemplo: en los microcontroladores de la serie PIC18F2455/2550/4455/4550/4553 sólo se implementan 8 bancos, o sea un total de 2048 registros.

#### 1.6.3.1 Registros de control

Como ya se indicó, los registros de control se encuentran ubicados en la parte superior del banco 15 de la memoria de datos (RAM) ordenados como se muestra en la tabla 1.3.

Cada uno de estos registros será utilizado según la necesidad, ya que existen registros de control para configurar cada periférico interno que se vaya a usar. Por ejemplo para configurar los puertos, se tienen los registros PORT, TRIS y LAT; si se desea utilizar el conversor analógico/digital, uno de los registros de control a usarse es ADCON. Los registros de control involucrados con cada periférico del microcontrolador, se detallan en el correspondiente "datasheet" además de los posibles valores a cargar en cada registro, según la configuración deseada.

| FFFh TOSU                    | FDFh INDF2 <sup>(1)</sup>    | FBFh CCPR1H                | F9Fh IPR1                 | F7Fh UEP15                  |

|------------------------------|------------------------------|----------------------------|---------------------------|-----------------------------|

| FFEh TOSH                    | FDEh POSTINC2 <sup>(1)</sup> | FBEh CCPR1L                | F9Eh PIR1                 | F7Eh UEP14                  |

| FFDh TOSL                    | FDDh POSTDEC2 <sup>(1)</sup> | FBDh CCP1CON               | F9Dh PIE1                 | F7Dh UEP13                  |

| FFCh STKPTR                  | FDCh PREINC2 <sup>(1)</sup>  | FBCh CCPR2H                | F9Ch —(2)                 | F7Ch UEP12                  |

| FFBh PCLATU                  | FDBh PLUSW2 <sup>(1)</sup>   | FBBh CCPR2L                | F9Bh OSCTUNE              | F7Bh UEP11                  |

| FFAh PCLATH                  | FDAh FSR2H                   | FBAh CCP2CON               | F9Ah —(2)                 | F7Ah UEP10                  |

| FF9h PCL                     | FD9h FSR2L                   | FB9h <u>(2)</u>            | F99h —(2)                 | F79h UEP9                   |

| FF8h TBLPTRU                 | FD8h STATUS                  | FB8h BAUDCON               | F98h —(2)                 | F78h UEP8                   |

| FF7h TBLPTRH                 | FD7h TMR0H                   | FB7h ECCP1DEL              | F97h —(2)                 | F77h UEP7                   |

| FF6h TBLPTRL                 | FD6h TMR0L                   | FB6h ECCP1AS               | F96h TRISE <sup>(3)</sup> | F76h UEP6                   |

| FF5h TABLAT                  | FD5h T0CON                   | FB5h CVRCON                | F95h TRISD <sup>(3)</sup> | F75h UEP5                   |

| FF4h PRODH                   | FD4h(2)                      | FB4h CMCON                 | F94h TRISC                | F74h UEP4                   |

| FF3h PRODL                   | FD3h OSCCON                  | FB3h TMR3H                 | F93h TRISB                | F73h UEP3                   |

| FF2h INTCON                  | FD2h HLVDCON                 | FB2h TMR3L                 | F92h TRISA                | F72h UEP2                   |

| FF1h INTCON2                 | FD1h WDTCON                  | FB1h T3CON                 | F91h —(2)                 | F71h UEP1                   |

| FF0h INTCON3                 | FD0h RCON                    | FB0h SPBRGH                | F90h —(2)                 | F70h UEP0                   |

| FEFh INDF0 <sup>(1)</sup>    | FCFh TMR1H                   | FAFh SPBRG                 | F8Fh(2)                   | F6Fh UCFG                   |

| FEEh POSTINCO(1)             | FCEh TMR1L                   | FAEh RCREG                 | F8Eh —(2)                 | F6Eh UADDR                  |

| FEDh POSTDECO <sup>(1)</sup> | FCDh T1CON                   | FADh TXREG                 | F8Dh LATE <sup>(3)</sup>  | F6Dh UCON                   |

| FECh PREINCO <sup>(1)</sup>  | FCCh TMR2                    | FACh TXSTA                 | F8Ch LATD <sup>(3)</sup>  | F6Ch USTAT                  |

| FEBh PLUSW0 <sup>(1)</sup>   | FCBh PR2                     | FABh RCSTA                 | F8Bh LATC                 | F6Bh UEIE                   |

| FEAh FSR0H                   | FCAh T2CON                   | FAAh(2)                    | F8Ah LATB                 | F6Ah UEIR                   |

| FE9h FSR0L                   | FC9h SSPBUF                  | FA9h EEADR                 | F89h LATA                 | F69h UIE                    |

| FE8h WREG                    | FC8h SSPADD                  | FA8h EEDATA                | F88h —(2)                 | F68h UIR                    |

| FE7h INDF1 <sup>(1)</sup>    | FC7h SSPSTAT                 | FA7h EECON2 <sup>(1)</sup> | F87h —(2)                 | F67h UFRMH                  |

| FE6h POSTINC1 <sup>(1)</sup> | FC6h SSPCON1                 | FA6h EECON1                | F86h —(2)                 | F66h UFRML                  |

| FE5h POSTDEC1(1)             | FC5h SSPCON2                 | FA5h(2)                    | F85h —(2)                 | F65h SPPCON <sup>(3)</sup>  |

| FE4h PREINC1 <sup>(1)</sup>  | FC4h ADRESH                  | FA4h(2)                    | F84h PORTE                | F64h SPPEPS <sup>(3)</sup>  |

| FE3h PLUSW1 <sup>(1)</sup>   | FC3h ADRESL                  | FA3h(2)                    | F83h PORTD <sup>(3)</sup> | F63h SPPCFG <sup>(3)</sup>  |

| FE2h FSR1H                   | FC2h ADCON0                  | FA2h IPR2                  | F82h PORTC                | F62h SPPDATA <sup>(3)</sup> |

| FE1h FSR1L                   | FC1h ADCON1                  | FA1h PIR2                  | F81h PORTB                | F61h — <sup>(2)</sup>       |

| FE0h BSR                     | FC0h ADCON2                  | FA0h PIE2                  | F80h PORTA                | F60h —(2)                   |

|                              |                              |                            |                           |                             |

|                              |                              |                            |                           |                             |

Tabla 1.3: Registros de propósito específico del microcontrolador

Fuente: PIC18F2455/2550/4455/4550 Data Sheet.

<a href="http://www.bilbaoelectronics.com/datasheet-pic18f4550.html">http://www.bilbaoelectronics.com/datasheet-pic18f4550.html</a> [Consulta: 17 de febrero de 2012]

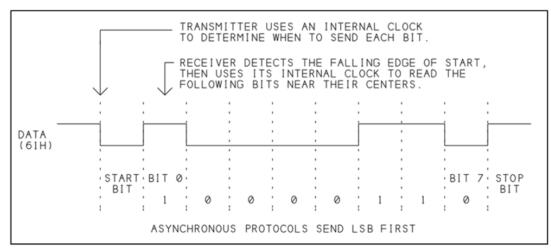

#### 1.6.4 Módulo EUSART

El EUSART ("Enhanced Universal Synchronous Asynchronous Receiver Transmitter") es uno de los dos módulos de comunicación serial que poseen los microcontroladores de Microchip. El mismo puede configurarse en 3 modos de trabajo diferentes:

- 1. Asincrónico o asíncrono ("full duplex").

- 2. Sincrónico Master ("half duplex").

- 3. Sincrónico Esclavo ("half duplex").

#### 1.6.4.1 Modo asíncrono

Este modo se utiliza para comunicación "punto a punto" con periféricos asíncronos (computadoras personales por ejemplo), en modo full duplex. Su funcionamiento no necesita de enlace de reloj entre los dispositivos que se comunican.

#### 1.6.4.2 Modo síncrono

Este modo se utiliza para comunicación con dispositivos síncronos (Memorias Seriales Externas por ejemplo). La comunicación en este modo es half duplex y dependiente del enlace físico del reloj.

Los pines asociados al funcionamiento del EUSART multiplexan sus funciones con los pines RC6 (TX) y RC7 (RX) del puerto C:

#### 1.6.4.3 Trasmisor asíncrono

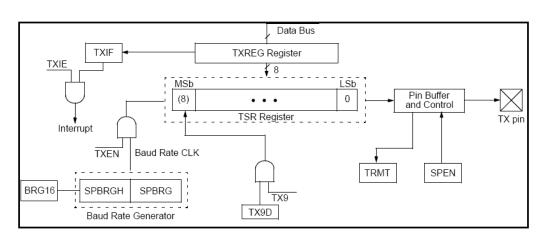

La estructura del hardware del trasmisor se muestra en la figura 1.12. La parte fundamental del trasmisor es el registro marcado como TSR ("Transmiter Shift Register"). El registro TSR es el encargado de "serializar el dato" que se carga en el "firmware" de forma paralela mediante el registro TXREG. La carga del TSR no se produce físicamente hasta que no se haya trasmitido el bit de "stop" de la trama previa.

La velocidad de desplazamiento de los bits cargados en el registro TSR es controlada por el Generador de Baudios ("Baud Rate Generator", BRG). El Generador de Baudios es un temporizador programable vía "firmware" que se dedica a garantizar la velocidad de trasmisión. Adicionalmente la trasmisión del noveno bit de datos se controla mediante dos bits (TX9 y TX9D) que conectan con una compuerta AND.

Figura 1.12. Diagrama de bloques del hardware del trasmisor

Fuente: PIC18F2455/2550/4455/4550 Data Sheet.

<a href="http://www.bilbaoelectronics.com/datasheet-pic18f4550.html">http://www.bilbaoelectronics.com/datasheet-pic18f4550.html</a> [Consulta: 17 de febrero de 2012]

### 1.6.4.4 Receptor asíncrono

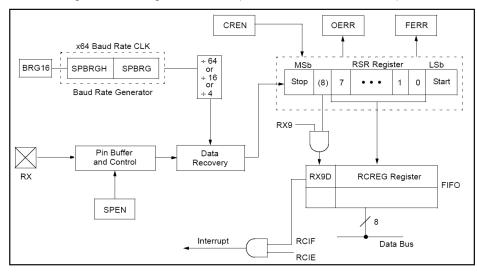

La estructura del hardware del receptor se muestra en la figura 1.13.

El dato se recibe en el pin RX e ingresa a un Registro de Desplazamiento temporal de alta velocidad ("Recovery Block"). El "Recovery Block" opera normalmente a 16 veces la velocidad de trasmisión programada. Al igual que el trasmisor, el receptor posee un registro de desplazamiento para la recepción (RSR). El RSR ("Receiver Shift Register") opera a la velocidad nominal del trasmisor.

Después del muestreo que el receptor realiza al pin RX en busca del bit de "stop", el dato recibido en el registro RSR se transfiere al Buffer de Recepción (registro RCREG). El registro RCREG físicamente es una memoria FIFO (First In First Out) de dos niveles. Lo que significa que se pueden almacenar hasta dos bytes recibidos. En caso de que se acumulen dos bytes, para extraerlos se debe leer dos veces el registro RCREG. Si no se leen los dos bytes almacenados y se termina de detectar el bit de STOP del tercero se perderá el último byte recibido (que se encuentra aún en el RSR) y se señalizará error de sobre escritura mediante el bit OERR (RCSTA <1>).

Figura 1.13. Diagrama de bloques del hardware del receptor

Fuente: PIC18F2455/2550/4455/4550 Data Sheet.

<a href="http://www.bilbaoelectronics.com/datasheet-pic18f4550.html">http://www.bilbaoelectronics.com/datasheet-pic18f4550.html</a> [Consulta: 17 de febrero de 2012].

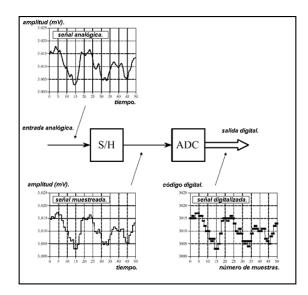

# 1.6.5 Conversor analógico/digital

Un convertidor analógico - digital es un dispositivo encargado de realizar los dos procesos necesarios para digitalizar una señal: muestreo y cuantificación. La estructura básica de un convertidor analógico - digital se muestra en la figura 1.14.

Figura 1.14. Diagrama del módulo AD

Fuente: PIC18F2455/2550/4455/4550 Data Sheet.

<a href="http://www.bilbaoelectronics.com/datasheet-pic18f4550.html">http://www.bilbaoelectronics.com/datasheet-pic18f4550.html</a> [Consulta: 17 de febrero de 2012]

El proceso de digitalización de una señal consiste de dos partes; el "Sample and Hold" captura la muestra y almacena su nivel de voltaje en un capacitor y el cuantificador (ADC) es el encargado de convertir la muestra almacenada en el capacitor del S/H en un código digital de "n" bits. Para el caso del microcontrolador es de 12 bits.

# 1.6.6 Módulo MSSP

El Módulo MSSP ("Master Syncronous Serial Port") es un interfaz serial síncrona que resulta útil para comunicarse con periféricos síncronos. Dentro de los periféricos con los que puede establecerse comunicación utilizando el MSSP se pueden citar los siguientes: memorias seriales, convertidores analógico – digitales, registros de desplazamiento, otros microcontroladores; entre otros.

El módulo MSSP puede trabajar en dos modos:

- 1. Modo S.P.I ("Serial Peripheral Interfaz"). El modo S.P.I permite la comunicación síncrona "full duplex", a diferencia de las posibilidades que ofrece el modo síncrono implementado para el EUSART. S.P.I es un estándar síncrono multipunto que permite la conexión de hasta 8 dispositivos como máximo a una velocidad máxima teórica de 2,1 megabits / segundo.

- Inter Integrated Circuit (I2C). El modo I2C a su vez soporta los siguientes modos: master, multi master y slave. I2C es un estándar síncrono multipunto que permite la conexión de hasta 40 dispositivos como máximo a una velocidad máxima teórica de 3,4 megabits / segundo.

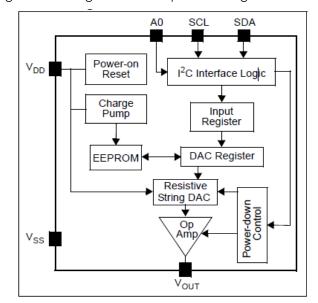

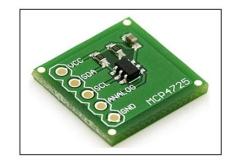

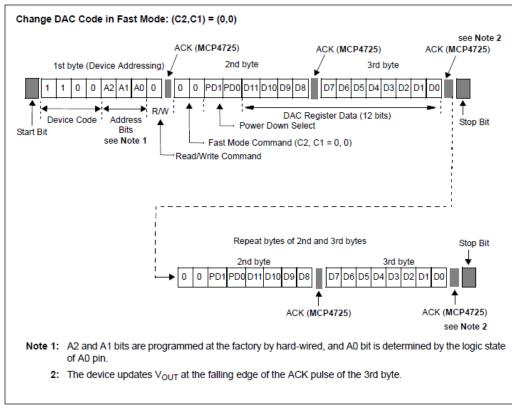

#### 1.7 Módulo MCP4725

El MCP4725 es un dispositivo integrado de bajo consumo y de alta precisión que nos permite la generación de una señal analógica a partir de valores discretos o capacidad de comunicación serial I2C. Este

conversor digital a analógico posee una resolución de 12 bits y una memoria EEPROM (no volátil).

El dispositivo posee un diseño reducido el cual se adapta fácilmente a entornos industriales pequeños, además de un modo de bajo consumo cuando se halla en reposo.

Tenemos además un rango de voltaje de operación que está comprendido desde los 2.7V hasta los 5.5V.

Además que posee un rango de temperatura para su funcionamiento establecido entre -40°C y 125°C.

## Aplicaciones:

- Calibración de sensores.

- Control servo de lazo cerrado.

- Instrumentación portable de bajo consumo.

- Sistemas de adquisición de datos.

Figura 1.14. Diagrama de bloques del integrado MCP4725

Fuente: 12-Bit Digital-to-Analog Converter with EEPROM Memoryin SOT-23-6 <a href="http://www.sparkfun.com/datasheets/BreakoutBoards/MCP4725.pdf">http://www.sparkfun.com/datasheets/BreakoutBoards/MCP4725.pdf</a> [Consulta: 17 de febrero de 2012]

## **CAPÍTULO 2 .DISEÑO DE HARDWARE**

#### Introducción

En este segundo capítulo se llevará a cabo el diseño del hardware correspondiente al módulo de adquisición y coordinador.

Se tomarán en cuenta para el diseño del PCB factores como:

- Protecciones contra sobre-voltajes para líneas de entrada analógica.

- Ubicación óptima de componentes.

- Diseño reducido y estético.

Además en lo concerniente al módulo de adquisición se debe diseñar considerando las siguientes características:

- Líneas Input analógicas.

- Líneas Input digitales.

- Líneas Output analógicas.

- Líneas Output digitales.

- Puerto serial.

- Puerto USB (para futuras aplicaciones).

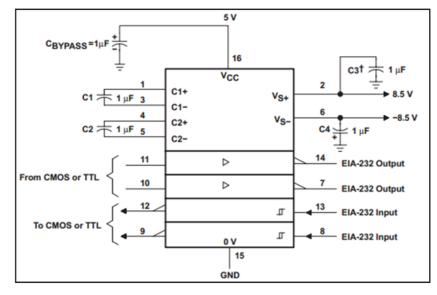

## 2.1 Esquema general módulo de adquisición y control

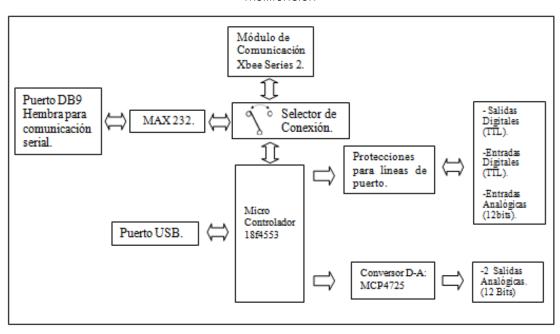

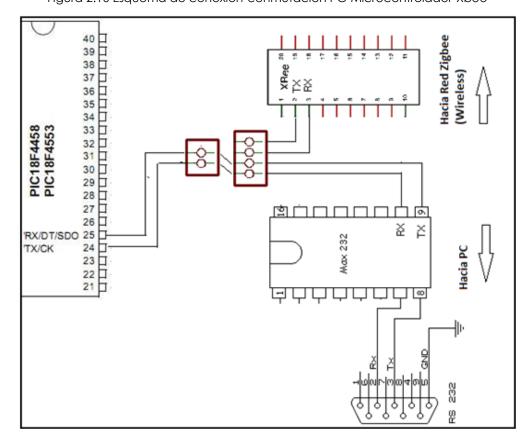

En lo referente a cantidad de líneas de puerto, en el módulo se proyecta 1 salida analógica, 8 salidas digitales, 5 pines doble función configurables como entrada o salida digital y 10 triple función programables como entrada digital, salida digital o entrada analógica según la necesidad, dando un total de 25 líneas de puerto disponibles. Conjuntamente con las líneas de entrada analógica se diseñan una serie de protecciones y comparadores que crean alarmas de sobre-voltajes. Adicionalmente a esto se considerará las capacidades de comunicación en dos tipos de protocolo RS232 y Zigbee. Todas estas características se detallan de manera general en la figura 2.1 y se desarrollaran a fondo en las diferentes secciones de este segundo capítulo.

Figura 2.1: Diagrama de bloques de módulo de adquisición y control inalámbrico multifunción

En cuanto al diseño del coordinador la implementación es más sencilla, ya que el coordinador únicamente poseerá conexión alámbrica mediante RS232 a una PC y conexión inalámbrica punto-punto o de broadcast a diferentes dispositivos de adquisición mediante Zigbee por lo cual el router tendrá los siguientes componentes:

- Módulo Xbee S2

- MAX232

- Puerto DB9

- Elementos para alimentación y regulación de voltaje

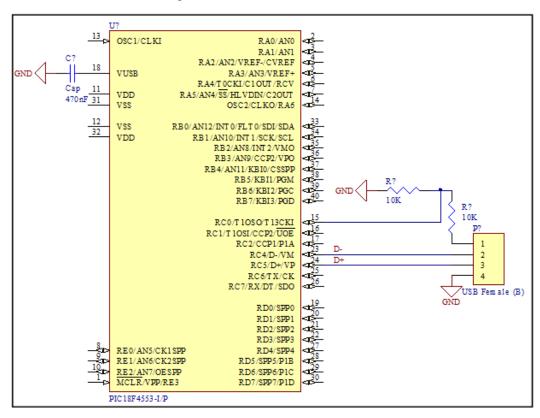

#### 2.2 Circuito básico de funcionamiento del microcontrolador 18f4553

Existen parámetros que previamente deben considerarse, dimensionarse y establecerse para que un microcontrolador funcione de manera adecuada, dichos parámetros están considerados como obligatorios en el desarrollo de cualquier hardware basado en microcontrolador y son:

- Alimentación

- Señal de reinicio

- Señal de Reloj

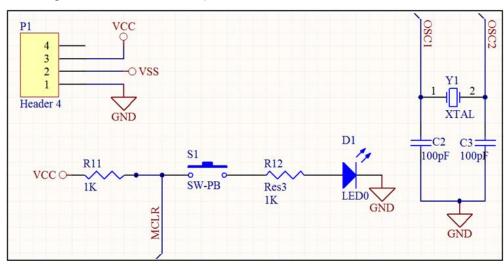

Figura 2.2 Circuitos básicos para el funcionamiento de microcontrolador

#### 2.2.1 Alimentación

En lo referente a la alimentación es necesario el uso de una fuente externa que proporcione + 5V DC, -5V DC y la referencia a tierra o GND para el correcto funcionamiento del microcontrolador y elementos como amplificadores operacionales, etc. Se implementará en el PCB un conector molex tipo macho, el mismo que mediante un bus de 3 vías llevara dichas señales de alimentación.

#### 2.2.2 Señal de reinicio

Para que un microcontrolador pueda funcionar apropiadamente, un uno lógico (VCC) se debe colocar en el pin de reinicio. En muchos casos el switch que conecta el pin MCLR a GND no es necesario; sin embargo, este botón casi siempre se implementa ya que habilita al microcontrolador volver al modo normal de funcionamiento en caso de que alguna subrutina presente un comportamiento inesperado. Al pulsar sobre el botón RESET (S1), el pin MCLR se lleva un voltaje de 0V, el microcontrolador se reinicia, y la ejecución de programa comienza desde el principio. Una resistencia de 10k se utiliza para impedir un corto circuito a tierra al presionar este botón.

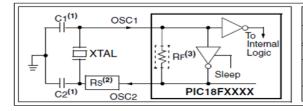

## 2.2.3 Señal de reloj

A pesar de tener un oscilador incorporado, el microcontrolador no puede funcionar sin componentes externos que estabilizan su funcionamiento y

determinan su frecuencia (velocidad de operación del microcontrolador), dependiendo de los elementos utilizados así como de las frecuencias, el oscilador puede funcionar en cuatro modos diferentes:

- 3 LP Cristal de bajo consumo

- 4 XT Crystal / Resonator

- 5 HS Cristal/Resonador de alta velocidad

- 6 RC Resistencia / Condensador

La configuración del circuito oscilador utilizado en este proyecto es: HS de 16 MHz, ya que, al ser una tarjeta de adquisición y control, se requiere alta velocidad en el procesamiento de datos y la frecuencia seleccionada es una de las mayores posibles.

En los modos HS, HSPLL, XT y XTPLL se debe conectar un cristal de quarzo a los pines OSC1 y OSC2 para establecer la oscilación. Además adicional al cristal de quarzo se necesitan conectar dos condensadores con determinados valores preestablecido para cada cristal. Los valores respectivos de cristales y condensadores están detallados en las hojas de especificaciones de cada microcontrolador o familia de los mismos.

Figura 2.3 Graficas de configuración de oscilador cerámicos, y tabla de cálculo de condensadores recomendados

| Typical Capacitor Values Used: |                     |                |                |  |  |  |  |

|--------------------------------|---------------------|----------------|----------------|--|--|--|--|

| Mode                           | Freq                | OSC1           | OSC2           |  |  |  |  |

| XT                             | 4.0 MHz             | 33 pF          | 33 pF          |  |  |  |  |

| HS                             | 8.0 MHz<br>16.0 MHz | 27 pF<br>22 pF | 27 pF<br>22 pF |  |  |  |  |

| Capacitor                      | values are fo       | r design guida | nce only.      |  |  |  |  |

Fuente: PIC18F2455/2550/4455/4550 Data Sheet.

http://ww1.microchip.com/downloads/en/DeviceDoc/39632e.pdf. [Consulta: 24 de febrero de 2012]

## 2.3 Protecciones para sobre-voltajes en pines I/O

Una característica fundamental en el módulo de adquisición es la facilidad que poseerán la mayoría de líneas de puerto para cumplir múltiples funciones, y nos referimos a múltiples ya que podrán con el uso de un código funcionar como entrada digital o analógica y como salida digital según sea la necesidad, esta característica es importante para tomar en

cuenta diferentes consideraciones en lo referente a protecciones contra sobre-voltajes y corrientes peligrosas.

La propiedad de bidireccionalidad de las líneas de puerto del módulo determinará el uso de una serie de componentes electrónicos y la realización de determinadas pruebas y simulaciones de funcionamiento de cada uno de estos componentes.

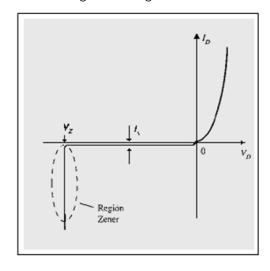

#### 2.3.1 Diodo Zener

Basándonos en el comportamiento de un diodo semiconductor de Silicio se observa la existencia de una zona en la cual, al aplicar un voltaje excesivo ocasiona un cambio drástico en las características, en este punto, la corriente se incrementa rápidamente con una dirección que se opone al sentido que denota la región del voltaje positivo. Los diodos Zener son elementos semiconductores que funcionan basados en esta región; de ahí su nombre. El voltaje de polarización inversa que provoca este cambio lo denominamos como Voltaje Zener.

Figura 2.4 Región Zener

Fuente: Electrónica teoría de circuitos y dispositivos electrónicos. Autor Boylestad Nashelsky.

[Consulta: 12 de Marzo de 2012]

El objetivo de utilizar estos diodos es el de limitar el voltaje de ingreso al microcontrolador cuando un puerto ha sido configurado como entrada analógica. Se debe considerar que un operario podría conectar un voltaje excesivo que supere los 5.3V que puede soportar el módulo de adquisición, lo cual haría que los elementos puedan averiarse parcial o totalmente. Se

ha optado como primer elemento de protección una resistencia en serie un diodo Zener en paralelo a cada una de las entradas.

El objetivo de esta protección es la siguiente:

- Aislar correctamente los componentes delicados de voltajes que los puedan dañar

- Utilizar los excesos de voltaje para crear alarmas sobre los mismos con el uso de componentes electrónicos y programación.

- Proporcionar una característica de bidireccionalidad segura al módulo de adquisición.

- Mantener un nivel de corriente estable y conocido en cada una de las entradas de puerto.

El uso del diodo Zener y la resistencia en serie al mismo, establecen los límites de voltaje de entrada tanto mínimos y máximos en los que el Diodo Zener inicia su funcionamiento o se destruye. EL límite inferior de funcionamiento se establece en 5.3 VDC y el límite máximo de alimentación de entrada que el Diodo puede soportar se establece en 53VDC.

Los cálculos relacionados a esos rangos se presentan a continuación, los datos obtenidos para IzM (corriente máxima) e IzK (Corriente mínima).

Se ha establecido el valor de la resistencia en serie en  $270\Omega$  ya que permite establecer un rango aceptable de alimentación.

Los siguientes son parámetros del diodo Zener 1N4733A obtenidos de hoja de datos [6]:

IzK = 1mA

IzM = 178mA

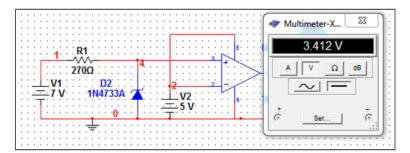

Figura 2.5 Esquema de circuito de protección.

[6]: http://www.datasheetcatalog.org/datasheet/fairchild/1N4733A.pdf

Vin = VRz + Vz

Vin = Iz\*Rz + Vz

Para el caso de voltaje mínimo de funcionamiento

Vin (min) = IzK \* Rz + Vz

$Vin(min) = 1mA * 270\Omega + 5.1$

Vin(min) = 5.37 V

Para el caso de voltaje máximo de ruptura

Vin (max) = IzM\* Rz+ Vz

Vin (max) = 178mA \*  $270\Omega + 5.1$

Vin (max) = 53.06 V

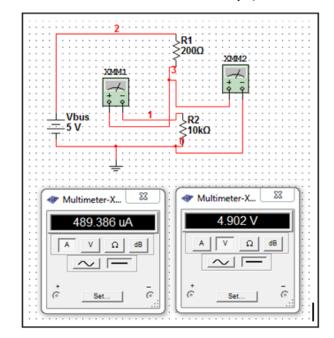

En la figura 2.5 se ha representado esquema sobre el cual se realizo los cálculos correspondientes a los voltajes mínimo y máximo. Además servirá como punto de partida para la simulación del comportamiento de los componentes implicados frente a un voltaje de entrada cambiante desde 1V hasta 12 V. Se realizó esta simulación en Multisim® 10®.

Se obtuvieron los datos procedentes de la simulación los cuales se muestran en la tabla 2.1 que consta de:

- Voltaje de Ingreso (V).

- Voltaje en el Diodo Zener (Vz).

- Voltaje en la Resistencia (Vr).

- Intensidad presente en el circuito (I).

A continuación se analizarán las gráficas resultantes de la simulación:

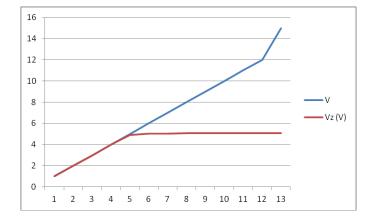

En la Figura 2.6 se observar que el comportamiento del voltaje en el Diodo Zener (Vz) es el esperado, debido a que mientras aumenta el voltaje de ingreso (V) de 0 a 5 voltios nuestra señal ingresa de manera estable con una pérdida prácticamente despreciable en la resistencia en serie.

Esta pérdida no afecta la calidad de la señal que se adquirirá por el canal analógico.

|    | Vz (V) | Vr (V)    | I(A)     |

|----|--------|-----------|----------|

| 1  | 1      | 0         | 0        |

| 2  | 2      | 0         | 0        |

| 3  | 3      | 0,0000088 | 0        |

| 4  | 4      | 0,000021  | 0        |

| 5  | 4,9    | 0,046     | 0,000172 |

| 6  | 5,032  | 0,967     | 0,00358  |

| 7  | 5,05   | 1,95      | 0,00722  |

| 8  | 5,061  | 2,93      | 0,0108   |

| 9  | 5,068  | 3,93      | 0,0145   |

| 10 | 5,07   | 4,926     | 0,0182   |

| 11 | 5,078  | 5,921     | 0,02192  |

| 12 | 5,083  | 6,97      | 0,0256   |

| 15 | 5,092  | 9,908     | 0,0366   |

Tabla 2.1. Datos recopilados de la simulación del circuito de protección

Posteriormente notamos que aunque el voltaje de entrada asciende el voltaje que envía el Diodo Zener hacia el microcontrolador se mantendrá casi constante ya que su variación es despreciable.

Se realizó simulación y se obtuvo que dentro del intervalo de 5 a 15 voltios de señal de ingreso el diodo Zener vario menos de 0,2 V.

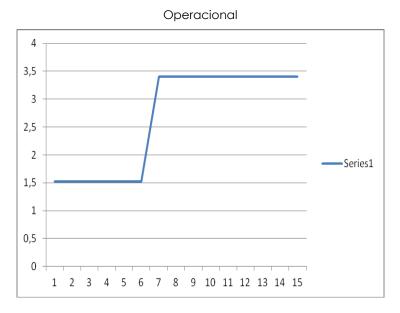

Figura 2.6 Grafica de Voltaje de ingreso Vs. Voltaje en el diodo Zener

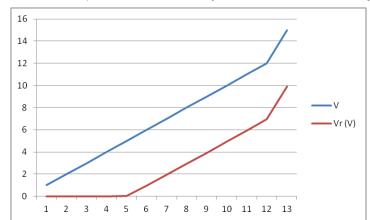

En la Figura 2.6 se observa el comportamiento en función del voltaje que experimenta la resistencia en serie, al igual que en lo anterior se dividirá en dos intervalos.

En el intervalo de 0 a 4V de señal de ingreso el voltaje presente en la resistencia va desde 0 a 21 uV el cual es un rango muy pequeño.

A partir de los 5 voltios se observa que se comporta de una manera totalmente diferente, el voltaje residual entre la entrada y el Zener en pleno funcionamiento se encuentra en esta resistencia. Usando este potencial se puede crear una señal de alarma ya que cuando la señal de ingreso ha sobrepasado el límite de 5V la señal en la resistencia será lo suficientemente grande como para entrar en un circuito de comparación, que será explicado posteriormente.

Figura 2.7 Grafica de comportamiento de Voltaje en la resistencia vs Voltaje de ingreso

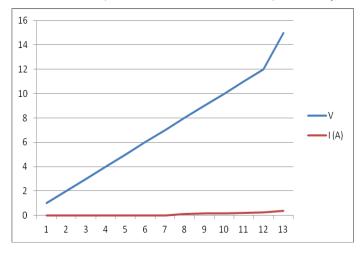

Debido al tipo de señal que el módulo usará y a la potencia que poseerá la misma, la corriente podría ser un factor que no representaría un mayor riesgo, pero de igual manera se realizó una simulación para determinar cuál es el rango de variación en una entrada que oscila desde 0 a 15 voltios y se obtuvo que la corriente máxima será de 36mA.

Al recopilar datos de las hojas de especificaciones del diodo Zener y observar en la I máxima que este componente puede soportar, se determina que está muy lejos de una corriente que lo pueda dañar ya que el valor que denota es de 178mA y solo sobrepasando esta corriente dañaríamos el diodo y podríamos poner en peligro el microcontrolador.

Figura 2.8 curvas de comportamiento de la Corriente y del voltaje de ingreso

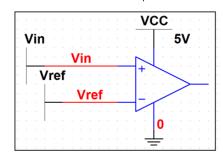

## 2.3.2 Comparador de voltaje

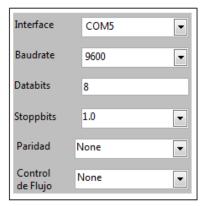

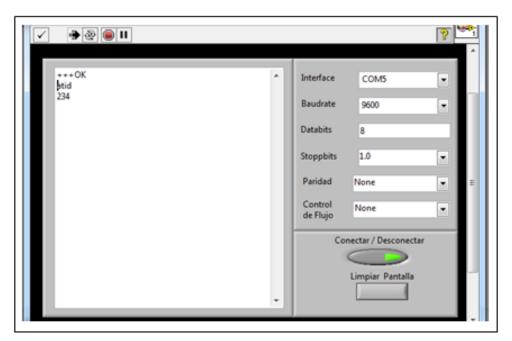

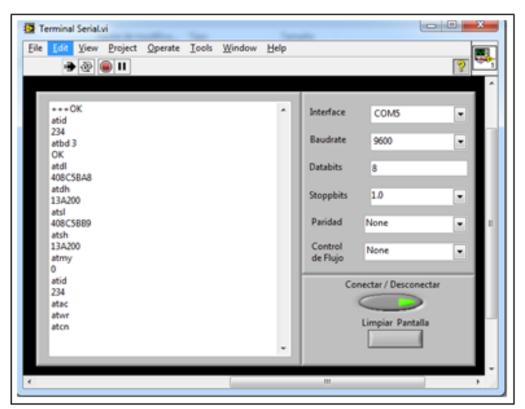

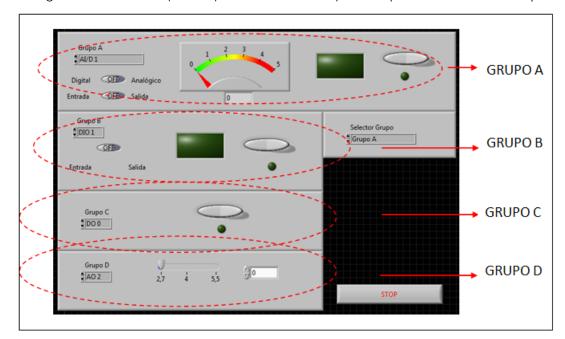

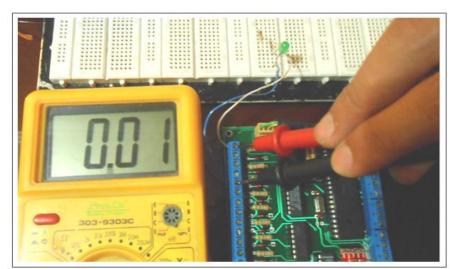

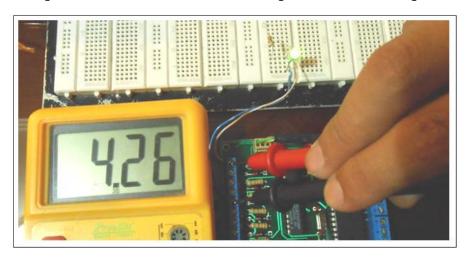

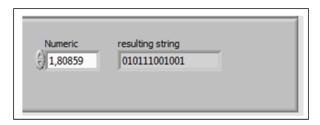

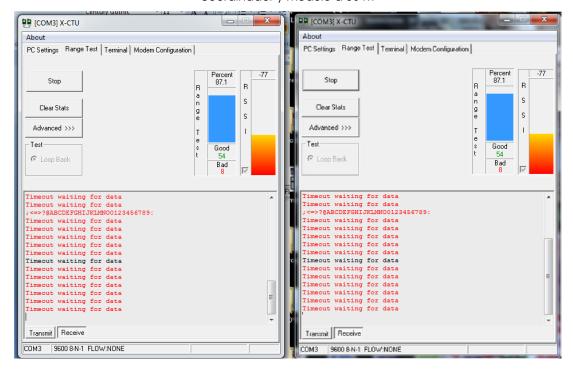

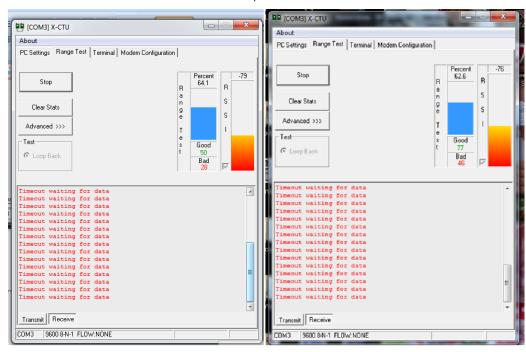

Debido a la necesidad de limitar el voltaje de entrada hacia los puertos del módulo de adquisición, se establece el uso de un circuito comparador de voltaje que tomará el voltaje de ingreso y lo contrastará con un voltaje de referencia previamente establecido, con el fin de emitir una señal que posteriormente pueda ser usada para informar acerca de una sobre-tensión presente en alguno de los pines configurados como entrada analógica, con esta alarma el usuario deberá tomar acciones correctivas y revisar las entradas que podrían presentar este voltaje peligroso.